# **Asian Journal of Applied Research**

DOI: http://dx.doi.org/10.20468/ajar.2018.10.11

# **Research Article**

# **Sequential Loading of Backup Generator with Load Sharing**

# P. K. Arun Kumar<sup>1</sup>, S. Venkatanarayanan<sup>2</sup>, R. Pragadeesh<sup>1</sup>, S. Nikhil<sup>1</sup>, R. Prasanna<sup>1</sup>, A. Prasanna Venkatesh<sup>1</sup>, S. M. Kannan<sup>2</sup>

<sup>1</sup>Department of Electrical and Electronics Engineering, Saranathan College of Engineering, Tiruchirappalli, Tamil Nadu, India, <sup>2</sup>Department of Electrical and Electronics Engineering, K.L.N. College of Engineering, Pottapalayam, Tamil Nadu, India

## ABSTRACT

In this project, we aim to rationalize and sequentially switch "ON" domestic loads during the power failure. The generator supply is rationalized to certain pre-set value per house. Generator side connections include household base loads and common area loads. During the power failure, the generator loads are sequentially switched "ON" which limits the starting current. High starting current affects the generator. Thus, switching system switches "ON" the loads sequentially with a steady time delay to limit the inrush current in this odd condition. The controller circuit is designed which sequentially loads the generator; this reduces the starting current. It includes a warning circuit which alerts the personnel when a power failure occurs. The system alerts when the load exceeds the pre-set value per house by alarm for few moments followed by system trips at the particular house. The house regains the generator power, once the load value is equal to or less than the pre-set value. The current consumption data of each household is logged and with the help of the collected data a real-time graph is plotted. The logged data can be used for future predictions of power failure with the suitable statistical model.

#### **INTRODUCTION**

In this fast-paced life of ours, the use of electric power and electric equipments is increasing at high speed. However, sufficient electric power is not available in many developing countries to fulfill the increasing need. The suppliers have to distribute this small amount of power all over the country. As a result, load shedding problem occurs. Due to this loadshedding, the irregular ON-OFF of the main power happens. This is where the use of generator comes into place when the power resumes through the generator almost all of us must have noticed the momentary dimming of the lights. This occurs when various load connections connected to the generator is switched ON simultaneously. The current drawn is so high that there is a chance of damaging the generator. We have succeeded to overcome this problem by implementing a switching system. The switching system switches "ON" the loads one after another with a regular time delay to avoid the limiting inrush current in the generator. The time delay can be varied by changing the clock frequency of the counter used in the circuit.

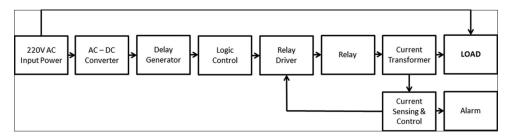

Moreover, we are going to pre-set value for the load consumption. If the number of loads switched ON fails to full fill this pre-set value an alert, with the help of an alarm for few moments followed by system trip at that particular house. The house regains the generator power, once the load value is equal to or less than the pre-set value. The block diagram of the system is shown in Figure 1. The paper is organized as follows: Section 2 presents related works and background study concerning switching system. Section 3 describes the circuit analysis of the proposed switching system. Section 4 presents the results and a brief discussion on the work and section 5 concludes this paper.

# **RELATED WORKS AND METHODS**

The switching system to control home appliances is a concerning topic in recent days. The work of Ajanta Palit<sup>[1]</sup> is about a switching system that turns "ON" the loads sequentially. The work referenced by Chowdhury<sup>[2]</sup> is about a remote controlled switching system with a sequential power "ON" attribute by Chowdhury *et al.* The remote-controlled switching system has great popularity as it can be controlled from a recommended distance easily.

### **CIRCUIT ANALYSIS**

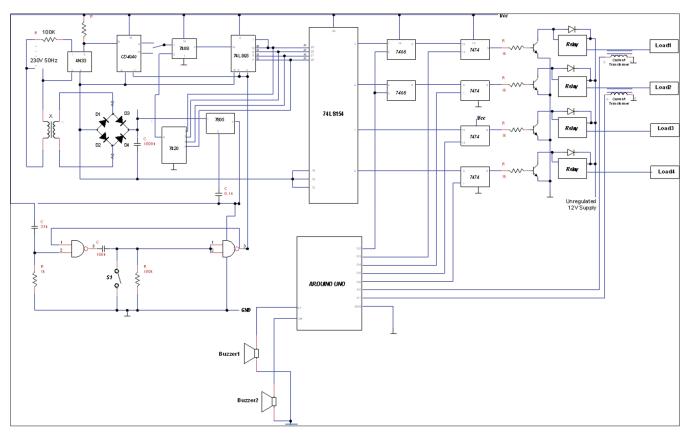

Figure 2 shows the circuit diagram of the complete switching system with a sequential power "ON" attribute. It comprises Optocoupler (4N33), decade counter (74LS93), divide-by-12 counter (CD4040), divide-by-16 counter

Copyright ©2018. The Author(s). Published by Arunai publications private Ltd.

E This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/)

# Address for correspondence:

P K. ArunKumar, Department of Electrical and Electronics Engineering, Saranathan College of Engineering, Tiruchirappalli, Tamil Nadu, India.

Keywords: Generator,

Power sharing, Relay, Sequential loading

Received: 05<sup>th</sup> February 2018 Accepted: 20<sup>th</sup> September 2018 Published: 13<sup>th</sup> October 2018 (74LS93), 1-of-16 decoder (74LS154), set-reset flip-flop (74LS74), NAND gate (74LS00), regulator (7805), relay switches, Quad-input NAND (74LS20), onboard precision current transformer, ARDUINO UNO board, and a few discrete components. AC mains operating frequency is 50Hz, which is isolated through optocoupler (4N33). For better understanding, the circuit descriptions are divided into the following sections as in the block diagram shown in Figure 1.

# AC to DC converter

The 220V, 50Hz AC main power is connected to the step-down transformer (X) and the optocoupler (IC- 4N33) in a parallel connection. The 12V, 500 mA output from the secondary winding of the transformer is fed to a full-wave bridge rectifier to convert AC into DC. The rectified output is then filtered to get fewer ripples. The unregulated 12V DC voltage is applied to a 5V DC regulator (IC-7805) to get a regulated 5V.

# **Delay generator**

Optocoupler (IC-4N33) consists of a gallium-arsenide infrared LED and a silicon photo-Darlington transistor. AC main power is connected to pin 1 of optocoupler through currentlimiting resistor R1. During the positive half cycle, the internal LED of the optocoupler is "ON," and the phototransistor is driven into saturation, and pin 5 goes low. The sinusoidal wave is converted into a square wave by this process. Thus, IC provides clock pulse for IC (CD4040) at pin 10. The C 4040 is a 12-stage ripple-carry binary counter. The counter advances by one count on the negative transition of each clock pulse. It resets to zero with a logical "high" at the reset input, independent of the clock pulse. Each counter stage is a static toggle flip-flop. Counter (CD4040) further divides the 50Hz clock frequency by 128 and 256. Output pin 4 and 13 provides clock pulse after an interval of 2.5 and 5 s, respectively, and also drives IC (74LS93).

## Logic control

The IC (74LS93) is a 4-bit binary ripple counter. It consists of 4 master-slave flip-flops internally connected to provide a divide-by-2 section and a divide-by-8 section. Each section has a separate clock input ( $\overline{CP0}$  and  $\overline{CP1}$ ) to initiate state changes of the counter on the "high" to "low" clock pulse transition. An AND gated asynchronous master reset (pins 2 and 3) is provided, which resets all the flip-flops. Since the output from the divide-by-2 sections is not internally connected to the succeeding stages in a 4-bit ripple counter, the Q0 output must be externally connected to CP1 input. The input count pulses are applied to the clock input CP0. Simultaneously, frequency divisions of 2, 4, 8, and 16 are performed at the Q0, Q1, Q2, and Q3 outputs, respectively. The outputs of 47LS93 provide the address inputs to 1-of-16 decoder IC (74LS154). The decoder 74LS154 accepts four active "high" binary address inputs (A0 through A3) and provides 16 mutually exclusive active "low" outputs (O0 through O15). The E0 and E1 inputs enable the gates which can be used either to strobe the decoder for eliminating the normal decoding glitches on the outputs or for expansion of the decoder. The enable gate has two ANDed inputs which are made "low" (by connecting them to ground) to enable the outputs.

### **Relay driver**

The 74LS74 is a dual, positive-edge-triggered, D-type flipflop featuring individual data, clock signal, set-reset inputs as well as true and complementary outputs. Set (S) and reset inputs (R) are asynchronous active "low" inputs that operate independently of the clock input. When reset input is "high" and set input is "low," the Q output goes "high" to energize the relay. When reset input is "low" and set input is "high," the Q output goes "low" to de-energize the relay. IC through IC (each 74LS74) is used as set-reset flip-flops to drive the relays with the help of transistors (T3 through T18). Arduino digital output pin [D2] (enable output) is ANDed with output pins (O0 and O2) of 74LS154 and is connected to SET pin of 74LS74. The purpose of this connection is to again SET the flip-flop in case of RESET. Another, digital output pins (D3, D4, D5, and D6) are connected to the RESET pin of 74LS74. The purpose of this connection is to RESET the flip-flop in case of load current exceeding the pre-set value.

#### Relay

The Q outputs of 74LS74 ICs are connected to the bases of transistors (T3 through T18) through resistors (R10 through R25), respectively. All the relays (RL2 through RL17) are connected to the collectors of transistors (T3 through T18), respectively. An unregulated 12V DC voltage is applied to the relay switches to provide energizing voltages for the relays. Diodes (D6 through D21) connected across relays (RL2 through RL17), respectively; act as free-wheeling diodes.

When output pin 5 of flip-flop 74LS74 (IC\_A) goes "high," transistor T3 is driven into saturation, and relay RL2 get energized. Similarly, the "high" Q output of other flip-flops drive relays (RL3 through RL17). Loads (LOAD 1–LOAD 16) are connected with the relays (RL2 through RL17), respectively, to control them. Here, in this circuit of Figure 2, we have

Figure 1: Block diagram

Figure 2: Circuit diagram

shown four loads as an example to give an idea about the load connections to the readers. One can connect 16 loads at a time with this switching system in the same manner. To avoid the random energizing of relays, power "ON" reset is achieved with NAND gate (IC-74LS00). The NAND gates are configured as monostable. Reset pins of IC and IC are connected to pin 6 of NAND gate N2. The output of N2 is inverted and connected to Arduino to RESET all the flip-flops. Switch S1 is used for manual reset.

### **Current Sensor**

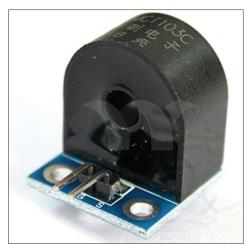

The device used as a current sensor in this case of ON-BOARD precision current transformer [0-5 V] which gives an output of 0–5 mv for an equivalent load current of 0–5 A [Figure 3].

# **Current Sensing Control and Alarm**

The first step in current sensing control is the conversion of analog signal to a digital signal by means of function to get the current drawn by the load.

Max Value = analog read (sensor 1); nVPP = (max Value \* 5.0)/1024.0; nCurrThruResistorPP = (nVPP/200.0) \* 1000.0; nCurrThruResistorRMS = nCurrThruResistorPP \* 0.707; nCurrentThruWire = nCurrThruResistorRMS \* 1000; Now, the measured value is compared with the pre-set value. When the measured current value is greater than the pre-set value, the digital pin of that particular relay driver is pulled low, so that the relay de-energizes. An Arduino pin [D7 and D8] is used to initiate the alarm for a predetermined time period. In case of an action not taken, the whole power supply would be cut off. To once again energize the relay again, the manual push button is used to pull the SET pin to ground.

# **Arduino UNO**

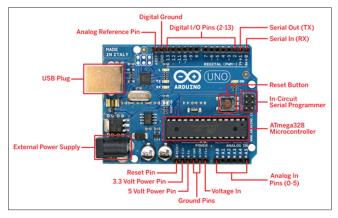

Arduino Uno is a microcontroller card which has ATmega328P [Figure 4]. The Arduino has 14 digital inputoutput (6 of them can be used for PWM), 6 analog input, a 16 MHz quartz crystal, a USB connection, a ICSP connection and are set button. Furthermore, it has 5V, 3.3V, GND, and VIN pins in the power side. The Arduino operation voltage is 5V. The input voltage can be between 7V and 12V. In this project, USB connection is used for power voltage. The Arduino can run with a 9V adaptor. As memory features, the Arduino has flash memory 32KB, SRAM 2KB, and EEPROM 1KB. Arduino IDE compiler is used to compile the Arduino code.

## **RESULTS AND DISCUSSION**

Procedures and precautions needed to construct the circuit of Figure 2 to obtain desired output are discussed in this section. The voltages and currents of all the branches of the circuit are measured carefully with a multimeter and recorded in Table 1. Table 1 describes different data found in different sections of

Figure 3: Onboard precision current transformer

Figure 4: Arduino UNO board

| Table 1: | Data | analysis | of the | switching | system |

|----------|------|----------|--------|-----------|--------|

|----------|------|----------|--------|-----------|--------|

the circuit. These data are significant for the proper analysis of the circuit. The resistances of the connecting wires are ignored so that they have no effect on the output. The electrical loads are connected to the 220V AC line carefully through relay contacts as shown in Figure 2 to avoid an accident. Mainsrated cable can be used for all load connections. The loads should switch "ON" sequentially with a time delay of 2.5 and 5 s. The manual reset switch (S1) is pressed if any of the four loads turns "ON" randomly after power resumption. The time delay can be changed by changing the input frequency of the clock pulse of a binary counter (74LS93). The optocoupler can be checked to have a pulse of 50Hz which provides the clock pulse for the divide-by-12 counter (CD4040). The 74LS90 or 74LS93 IC can be used instead of CD4040. The IC (CD4040) counter divides the pulse by 10 to provide clock pulse for binary counter (74LS93). The IC (74LS93) counter produces addresses for the 1-to-16 decoder (IC).

The outputs are checked using a digital planner board. The functionality of the flip-flops can also be checked by the digital planner board. Table 1 show that the transistors (T3-T18) are in saturation one after another with a time delay. The main power is disconnected while constructing the circuit to eliminate the risk of electrical shock. Providing completion of the circuit, main power is turned "ON" carefully. The loads are then turned "ON" one after another sequentially. The whole process is performed automatically by the circuit. If the loads are turned "ON" randomly rather than sequentially, then the reset pin is pressed to reset the logic ICs. Until the presence of EB power supply, current sensing and control block will be ideal.

In case of grid power failure, a manual changeover switch is used to connect the loads to the generator. At, this condition

| Input<br>frequency                | Frequency<br>across IC | Inputs of IC |    |    |     | Outputs<br>of IC | Saturated<br>transistor | Voltage across the saturated transistor |               | ON state of the switch |

|-----------------------------------|------------------------|--------------|----|----|-----|------------------|-------------------------|-----------------------------------------|---------------|------------------------|

|                                   |                        | <b>Q0</b>    | Q1 | Q2 | Q3  |                  |                         | Base (v)                                | Collector (V) |                        |

|                                   |                        | 0            | 0  | 0  | 0   | 00               | Т3                      | 3.22                                    | 0             | RL2                    |

|                                   |                        | 0            | 0  | 0  | 1   | $\overline{01}$  | T4                      | 3.22                                    | 0             | RL3                    |

|                                   |                        | 0            | 0  | 1  | 0   | 02               | Т5                      | 3.22                                    | 0             | RL4                    |

|                                   |                        | 0            | 0  | 1  | 1   | 03               | Т6                      | 3.22                                    | 0             | RL5                    |

|                                   |                        | 0            | 1  | 0  | 0   | 04               | Τ7                      | 3.22                                    | 0             | RL6                    |

|                                   |                        | 0            | 1  | 0  | 1   | 05               | Т8                      | 3.22                                    | 0             | RL7                    |

|                                   |                        | 0            | 1  | 1  | 0   | 06               | Т9                      | 3.22                                    | 0             | RL8                    |

|                                   |                        | 0            | 1  | 1  | 1   | 07               | T10                     | 3.22                                    | 0             | RL9                    |

|                                   |                        | 1            | 0  | 0  | 0   | $\overline{08}$  | T11                     | 3.22                                    | 0             | RL10                   |

| 50 Hz 0.1953 Hz (or)<br>0.3968 Hz | 1                      | 0            | 0  | 1  | 09  | T12              | 3.22                    | 0                                       | RL11          |                        |

|                                   | 1                      | 0            | 1  | 0  | 010 | T13              | 3.22                    | 0                                       | RL12          |                        |

|                                   | 1                      | 0            | 1  | 1  | 011 | T14              | 3.22                    | 0                                       | RL13          |                        |

|                                   | 1                      | 1            | 0  | 0  | 012 | T15              | 3.22                    | 0                                       | RL14          |                        |

|                                   | 1                      | 1            | 0  | 1  | 013 | T16              | 3.22                    | 0                                       | RL15          |                        |

|                                   |                        | 1            | 1  | 1  | 0   | 014              | T17                     | 3.22                                    | 0             | RL16                   |

|                                   |                        | 1            | 1  | 1  | 1   | 015              | T18                     | 3.22                                    | 0             | RL17                   |

current sensing and control unit monitors the current drawn by the load and performs the load shedding operation, in case of power margin violations.

#### CONCLUSIONS

The switching system discussed above is very effective in our daily life to save home appliances and to prevent impact loading of generators. It is clear from the above discussion that this switching circuit can be easily constructed as the circuit components are cheap and available in the market. The installation of the system is also easy.

The system is tested with four loads, and it provides the desired output. One can connect 16 loads with this switching system at a time. A switching system accommodating more than 16 loads can be constructed using the same concept.

#### REFERENCES

- 1. Palit A. Construction of Sequential Power 'ON' Circuit. Electronics for You; 2009. Available from: http://www.efymag.com.

- Chowdhury S, Alam D, Alam S. A remote controlled switching system with a sequential power 'ON' attribute. Int J Electron Electr Eng 2015;3:158-60.

- 3. Kharate GK. Digital Electronics. USA: Oxford University Press; 2012.

**Cite this article:** Kumar PKA, Venkatanarayanan S, Pragadeesh R, Nikhil S, Prasanna R, Venkatesh AP, Kannan SM. Sequential Loading of Backup Generator with Load Sharing. Asian J Appl Res 2018;4(2):56-60.

**Source of Support:** Nil, **Conflict of Interest:** None declared.